Modeling & Simulation technology company PI research LABO LLC

|

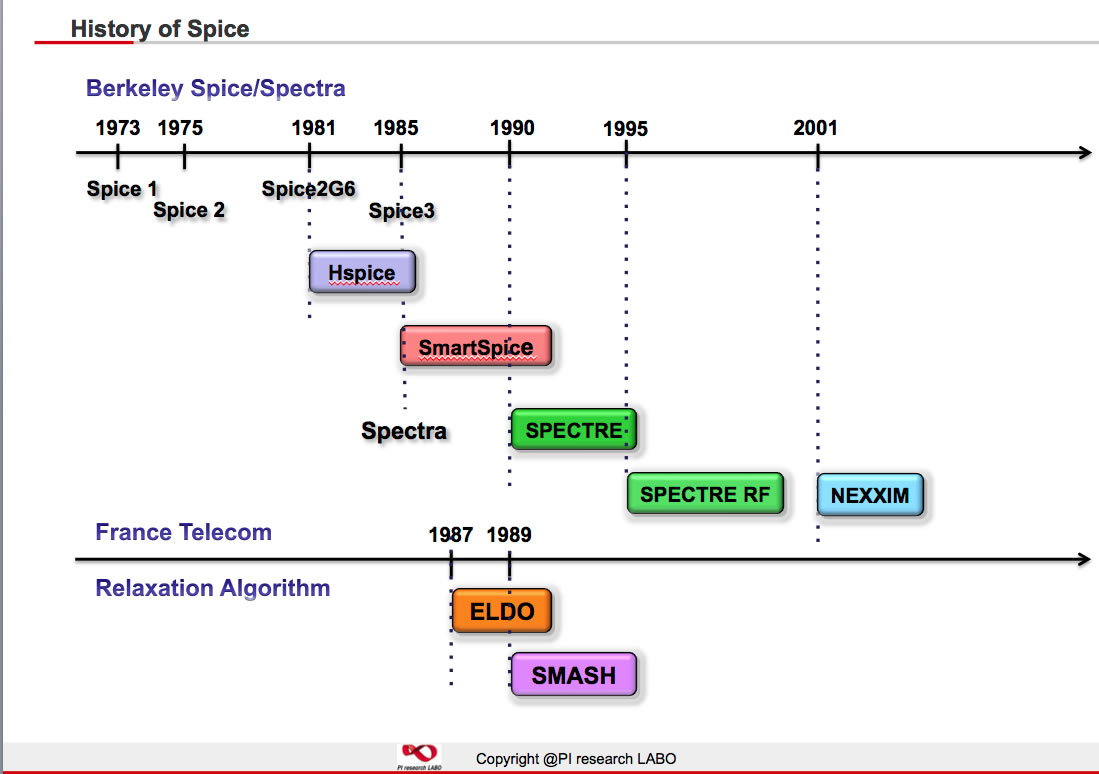

Spiceについて: 派生と歴史

最近、よく検索にひかかり、検索上位になって来ましたので真面目にSpiceの歴史と世に存在するSpiceの派生をひもときたいと思います。

現在Spice Simulatorと言われる物は、価格を記載するとVendorに怒られますので範囲で書きますが、安価な物で、19,800円の○○Spiceから上は、純粋なSpiceで約1000万の物まで様々です。どうしてこんなに価格が違うのか?PCBやオーディオのアマチュアの方にはさっぱりわからないと思います。価格の差=モデルの開発+Spiceの改良にお金がかかってるのです。Spiceのモデルと言うと、半導体設計をしてる人は、Bsim3やBsim4、そしてデバイスをしてる人や先端の人はPSPやHiSIM等のMOSモデル、高周波の設計者は、VBICやHiCUM等のBipolarモデル。TFTの設計者はRPIモデルとSpice modelがSimualtionする為に必要なのです。そして安いSpiceにもBsim3やBsim4が入ってますが、これらのモデルと、約1000万するSpiceのモデルは同じではありません。ソースコードは同じですが、各社がお金と人手をかけて改良しているのです。なので厳密に言うとA社のBsim4モデルとB社のBsim4モデルは違うのです。安価なSpiceとは全くと言っていいほど違います。違いが何故出てくるか?設計者になれば直ぐにわかります。なのですこれぐらいにして、Spiceも派生について以下表を載せてみます。

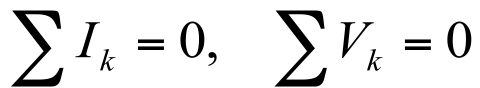

※ちなみに上の表のKCL/KVLは、Kirchhoff Current Law/Kirchhoff Voltage Lawの略です。

Berkeley Spiceをソースコードに持つPspiceやHspiceについては、良く知ってる方はいるかと思われますが、Spectreの大元について知ってられる方は非常に少ないのではと思います。実はHPとBerkely Univが共同でHB ( Harmonc Balance ) のSimulator(後のADS)を開発していた時の学生だったKen Kundart(当時)がCadenceに入社して作ったのが、Spectreでした。ちなみに記載にもありますようにADSのHBエンジンの開発呼称はSPECTRAでした。

一方でヨーロッパでは、フランスが強いです。やはり、旧France Telecomのプロジェクトで開発されたRelaxationアルゴリズムを持ったSimulatorを当時のANACAD社(現在Mentorに買収)が買い取り、ELDOとして世に出しました。一方でそのRelaxationアルゴリズムをベースに独自にSimulatorを作ったのがDolphin IntegrationのSMASHです。ちなみにこのアルゴリズムを使ったSimulatorは特徴的で、Spiceのオプションを見ればほぼわかります。現在ANSYSのSimplorerも同じではないかと思われます。(Hmin,Hmaxとかがあればほぼ間違いないと思われます)。

以下Berkeley SpiceとFrance Telecomのエンジン、そしてSpectreを年表にするとこんな感じになります。SPECTREの時期が微妙なんですが、Ken kundertが1989年にCadenceに入社してすぐに出たと記憶してますので多少の誤差はお許しください。

それでは、以下Spiceの技術を少しだけ紹介します。

spice simulation tips-1

一部Spice Simulation講座での内容をご紹介いたします。

1. Spice Simulationでの解法

HDLABの講座では、Spice SimulationのBeginner's/IntermediateそしてVerilog-AMSの

講座で以下の式が出て来ます。

これはKirchhoff(キルヒホッフ)の電流電圧の保存則で第一法則/第二法則と呼ばれる物です。

よくSpice 関連の書物やマニュアルではKCL, KVLと略されていますがこれの事をさしています。

※左のリンクには詳細をご紹介しています。続きは、spice simulation tips-1へ

spice simulation tips-2

一部Spice Simulation講座での内容をご紹介いたします。

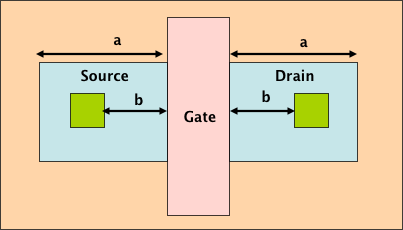

1. MOSの DIODEの面積計算

※MOSのダイオードの面積??と初めて耳にするSpice使用経験のある設計者の方へ、HSPICEを代表とする半導体設計で使用されるSPICE とPSPICEを初めとするPCB設計の安価なSPICEの違いはここにあります。

MOSにはDIODEモデルというものがあり、それによってMOSのSource/Drainの Diode部分の特性をSimulation結果に反映することができます。

- 特に重要なのがACM(Area Calculated Method)です。

- これによりSource/Drainの面積を計算し、Diode特性をSimulationしています。

ACM=0の時

上図とACM=0の時に使用するパラメータを示します。

- AD/AS : Area of Source/ Drain

- PD/PS : Peripheral (sidewall) of Source/Drain

- NRD/NRS : Number of Square resistance

- JS/JSW : Junction Current/Sidewall

- CJ/CJSW : Junction Capacitance/Sidewall

下図の場合トランジスタのゲート幅Wとして

- AD/AS = a*W

- PD/PS = 2*(a+W)

- NRD/NRS = b/W

として表す事ができます。

※左のリンクには詳細をご紹介しています。続きは、spice simulation tips2へ

spice simulation tips-3

一部Spice Simulation講座での内容をご紹介いたします。

1. transient noise simulation

Noise Simulationはアナログ/RF回路設計者にとっては必須でな解析です。近年CMOSの高性能化に よるデジタル回路とのMixed-Signal回路により過渡解析におけるNoise Simulation機能が搭載されています。これにより、従来PLLの解析で位相ノイズと呼ばれていました周波数ドメインの解析法であるHB(HarmonicBalance)解析でしか PLLのジッタを解析出来なかった物が、時間軸方向(タイムドメイン)でTransient Noise 解析によりノイズを付加したジッタ解析が出来るようになりました。近年でいえば、HDMI、USB3.0、さらには10GbEをベースにした 企画中のHDBase-TのLSIの設計では必須の解析です。 一般的にはTransient noise Simulationと呼ばれている機能で過渡解析において周波数ドメインの ノイズ成分をIFFTと疑似乱数を用いて各Simulationで解析されるデバイスに重畳しています。 (※各Simulatorによって詳細なアルゴリズムが違うので詳細は各Simulatorのマニュアルを参照ください)

2. 過渡ノイズ解析の出来るSpice Simulator

現在、この機能を搭載したSimulatorは以下です(順不同)

- Cadence : Spectre

- Synopsys : Hspice

- SILVACO: SmartSpice

- Dolphin Integration: Smash

- SIMetrix technology: SIMetrix

- Ansoft: NEXXIM

- BDA : AFS

ここでは、早期のこのtransient noise Simulation機能を搭載した二つのSimulator(SmashとSIMetrix)を使用したNoiseの精度を紹介します。 ※最後にAnsoftのNEXXIMの解析結果を追加しました(2009/12/28)

※左のリンクには詳細をご紹介しています。続きは、spice simulation tips3へ

spice simulation tips-4

一部Spice Simulation講座での内容をご紹介いたします。

1. Bsim3 NQSMODについて

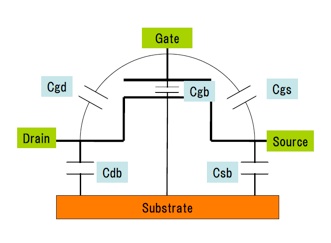

最近、Power Device についての問い合わせと依頼が多く、Blogにも書いてるのですが、Power Deviceには必須パラメータの一つで、通常のCMOSデバイスで使われていないパラメータがあります。 それが、C−V依存を反映させるFLAG:タイトルのNQSMODです。 これは、過渡解析においてC−Vの特性を反映させるFlagになっており、NQSMOD=1で有効になります。 しかしながら、これを使われた方いると思うのですが、Bsim3で収束させるのは至難の技です。 では、MOSのC-V特性をSimulationで見るにはどうしたらいいでしょう? おそらく、MOSのパラメータ抽出された方以外は知らないコマンドが出て来ますので良く学習しておいてください。 まずは、MOSの容量についてどんな容量があるか簡単に見てみます。右図を見てください。 右の容量が定義されているとします。

Hspiceではこの容量の計算のために、.optionで以下の記述をすればC−V特性を見る事ができます。

.option dccap

そしてMOSの各種容量にはlxで始まるエリアスが用意されており、各容量は以下のように表されます。

- .param cggbo=par('lx18(mp01)')

- + cgdbo=par('lx19(mp01)')

- + cgsbo=par('lx20(mp01)')

- + cbgbo=par('lx21(mp01)')

- + cbdbo=par('lX22(mp01)')

- + cbsbo=par('lX23(mp01)')

- .print dc cggbo cgdbo cgsbo cbgbo cbdbo cbsbo

※左のリンクには詳細をご紹介しています。続きは、spice simulation tips4へ