Modeling & Simulation technology company PI research LABO LLC

|

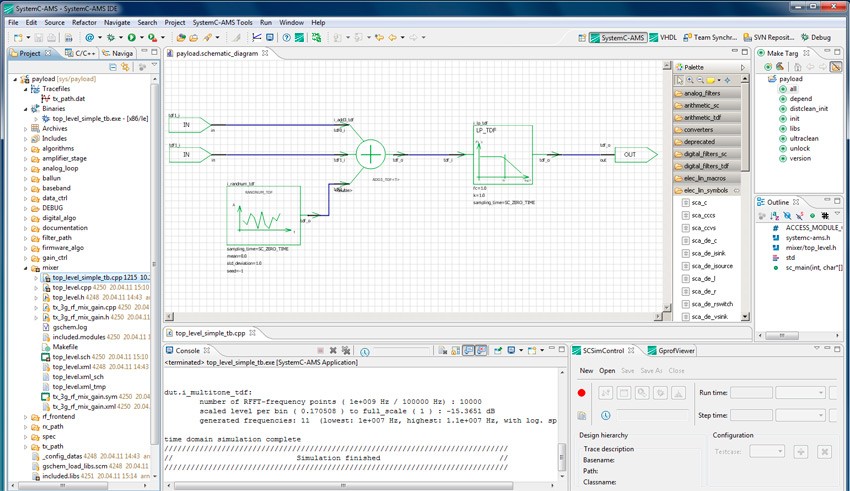

Fraunhofer IIS のSytemC AMS "COSIDE"の販売代理店権を獲得しました。

2013年9月 PI resrearch LABO,LLC とFraunhofer IISとの間で"COSIDE”に関する契約の全ての契約締結を完了いたしました。これから販売に向けて案内を配布いたしますので問い合わせ等おまちしております。

2000年からFraunhofer IIS/EASでは、SystemCを用いた研究開発をしてきております。

SystemC AMS IDE (SystemC AMS統合環境)"COSIDE"について

上記資料は以下からダウンロード出来ます

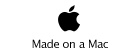

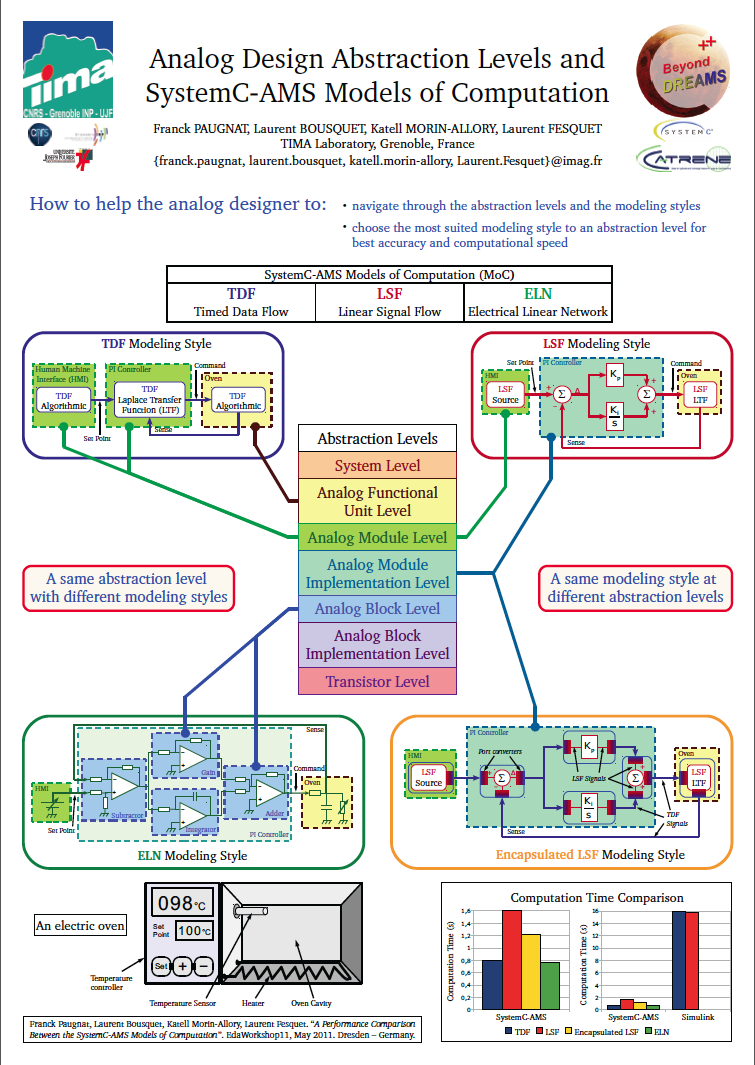

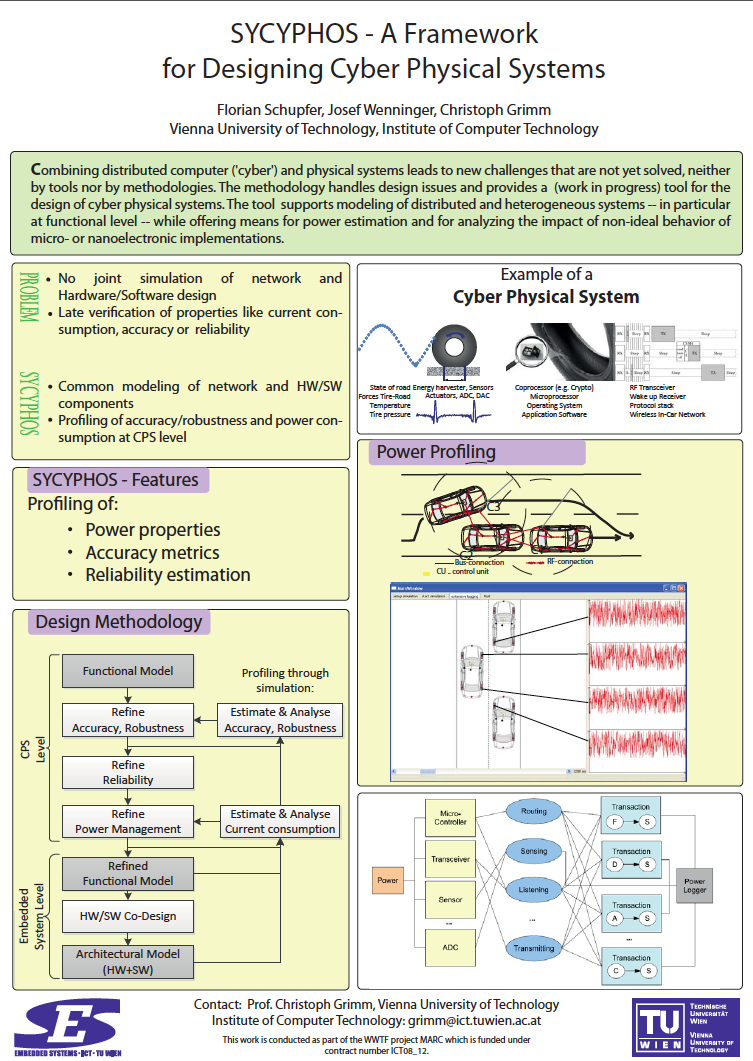

http://www.accellera.org/news/events/systemc_ams_day/systemc_ams_day_2011_postersession.pdf

COSIDEについてLinkを貼っておきますので各自資料をダウンロードしてみて下さい。

2004年発表資料ではまだSysmteCですが、次世代の車載システム要件について書かれています。

この時には既に、SystemCをtargetにしていたことが良くわかります。

http://www.systemc-ams.org/documents/FDL04_tutorial_final_10sep.pdf

SystemC AMS 2.0

ついにSystemC AMSのHPに概要とターゲットが明示されるようになりました。そして、SysmteC AMSの環境も同時にリリース。車載Simualation用のライブラリ:AK30のVHDL-AMSのモデルを作成&管理しているのは、ドイツのドレスデンに拠点を置きますフランファーワー研究所のIIS(Fraunhofer Institute for Integrated Circuits IIS,)ですが、SytemC AMSもフランフォーワ研究所所IISが管理しております。

SystemC AMSのHPはこちら:http://www.eas.iis.fraunhofer.de/en/business_areas/microelectronic_systems/system_development.html

そして、上のHPにはしっかりとターゲットにAutomotiveの図付き書かれています。

Why SystemC AMS?

- Extremely rapid simulation and verification of entire systems, including analog and digital hardware as well as software

- Effective verification of mixed-signal systems

- Handling of large models

- Support for various levels of abstraction

- Use of existing C / C++ libraries for mixed-signal system modeling

- Exchange of compiled models of mixed-signal systems, ensuring IP protection

ドイツや欧州では、次世代のSimulation環境の構築するために力を合わせて標準化に取り込んでいるのに、日本の自動車業界はは一昔の標準に縛られて、自ら開発標準化しようとしません。ここまでVHDL-AMSで今まさに…というのが日本ですが、もうヨーロッパはSystemC AMSなのです。

そして、もうSytemC AMSの環境も”COSIDE”という製品が出ています。

これから、AMSの環境を導入するならSystemC AMSではないでしょうか?

更に、Frainhofer IIS/EASからの資料では,既存のSimulatorに対して、

ある会社での実際のシステムSimulationにおいて、Real timeの1(s)にかかるSimulation時間は

1. Fast Sspice Simulator 1,000,0000,000(s)≒30(year)

2. Verliog-AMS/VHDL-AMS 10,000(s)≒1(day)

3. SystemC AMS: 4.0(s)

とSimulation時間に対して圧倒的なAdvantageを持ちます。

しかしながら、モデル作成の複雑さは増大しており、モデルを作成するには一苦労しそうです。

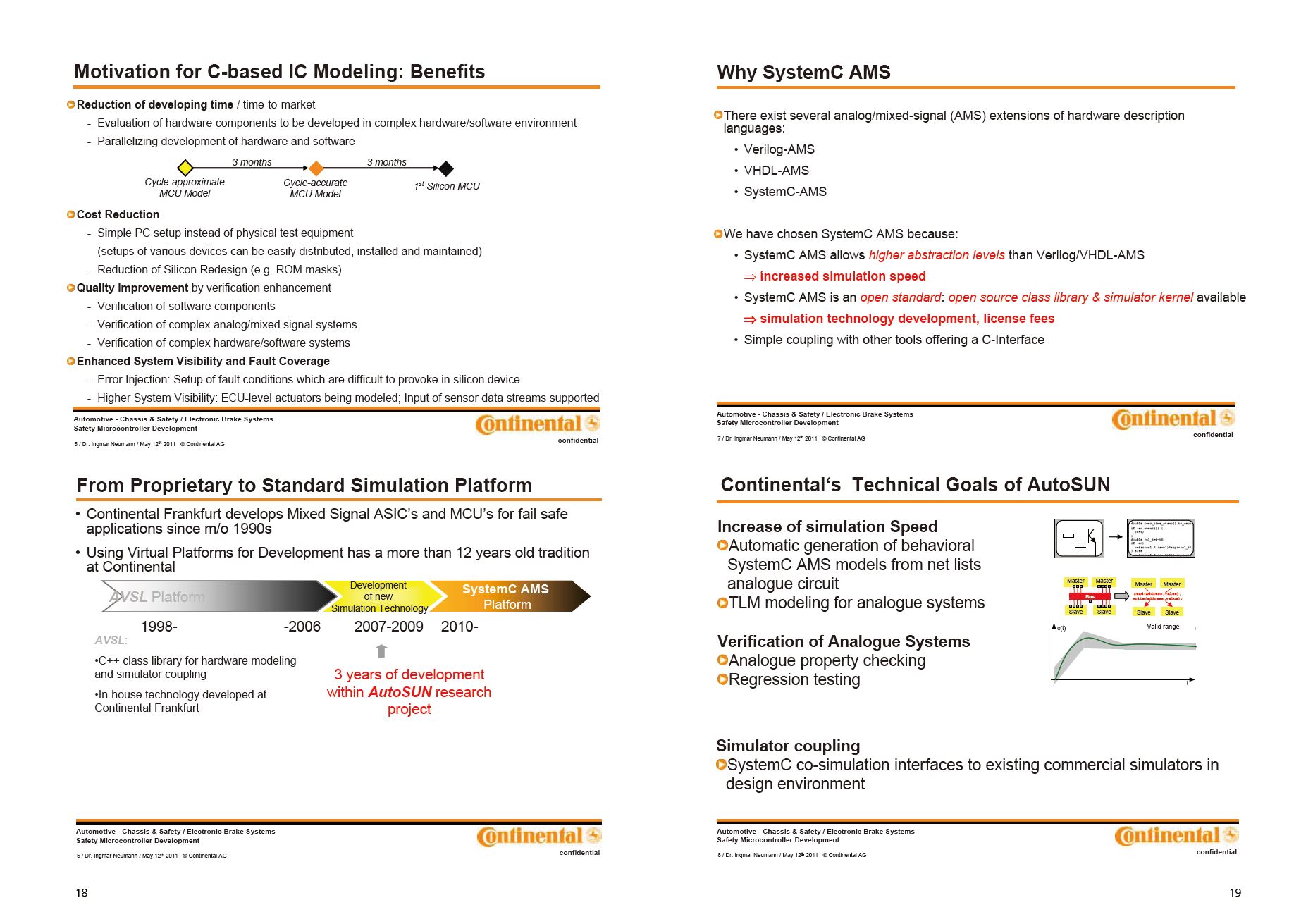

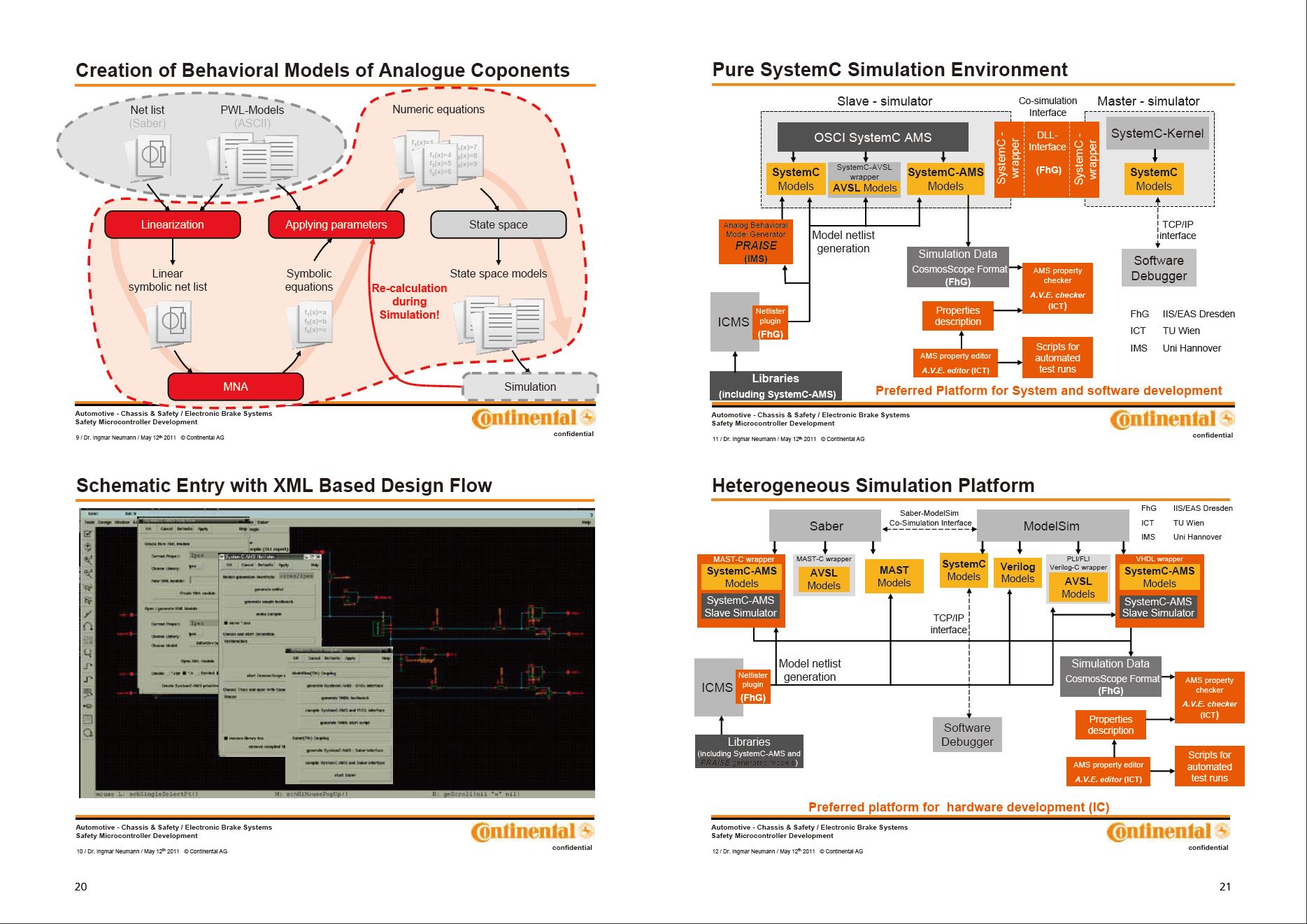

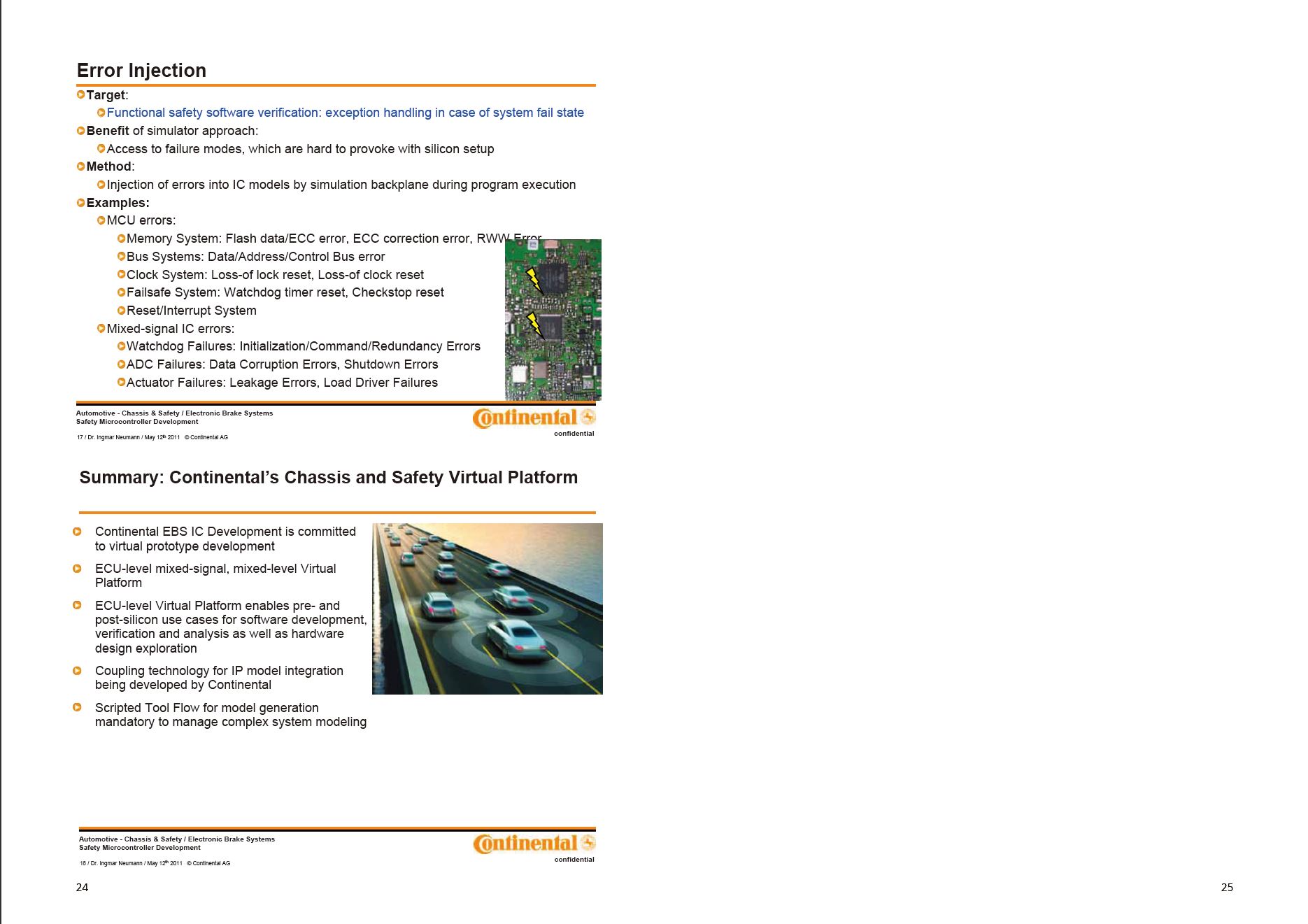

そして、昨年のContinental社の発表資料から

ちょっとはみ出ますが、お許しを。

この資料は、Blogでも紹介してますが、AccelleraのHPのSystemC AMSのdownloadサイトのLinkから落とせませすのでご参照ください。http://www.accellera.org/news/events/systemc_ams_day

次にP19の部分で何故SystemC AMSなのかをVerilog-AMS/VHDL-AMSと比較して述べています。

抜き出しますと;

We have chosen SystemC AMS because:

• SystemC AMS allows higher abstraction levels than Verilog/VHDL-AMS

⇒ íncreased simulation speed

• SystemC AMS is an open standard: open source class library & simulator kernel available

⇒ simulation technology development, license fees

• Simple coupling with other tools offering a C-Interface

さて、これからSystemの標準化がAMSで考えてる業界は間違ってもVHDL-AMSに進んでは駄目で、SystemC AMSに向かうべきです。ドイツの自動車業界はしっかり矛先を向けて標準化に向けて進んでいます。

Verilog-AMSとVHDL-AMS (VHDL-AMSユーザ必見)

Verilog-AMS/SystemVerilogとVHDL-AMSとAMSと呼ばれるものがありますが、最近さらにSystemC-AMSが加わり、かなりややこしくなって来たので、ここら辺で歴史を示して、整理してみます。また2011年にAccellera(EDA標準化団体)とOSCI(SystemCの普及団体)が統合され様相が変わって来ています。

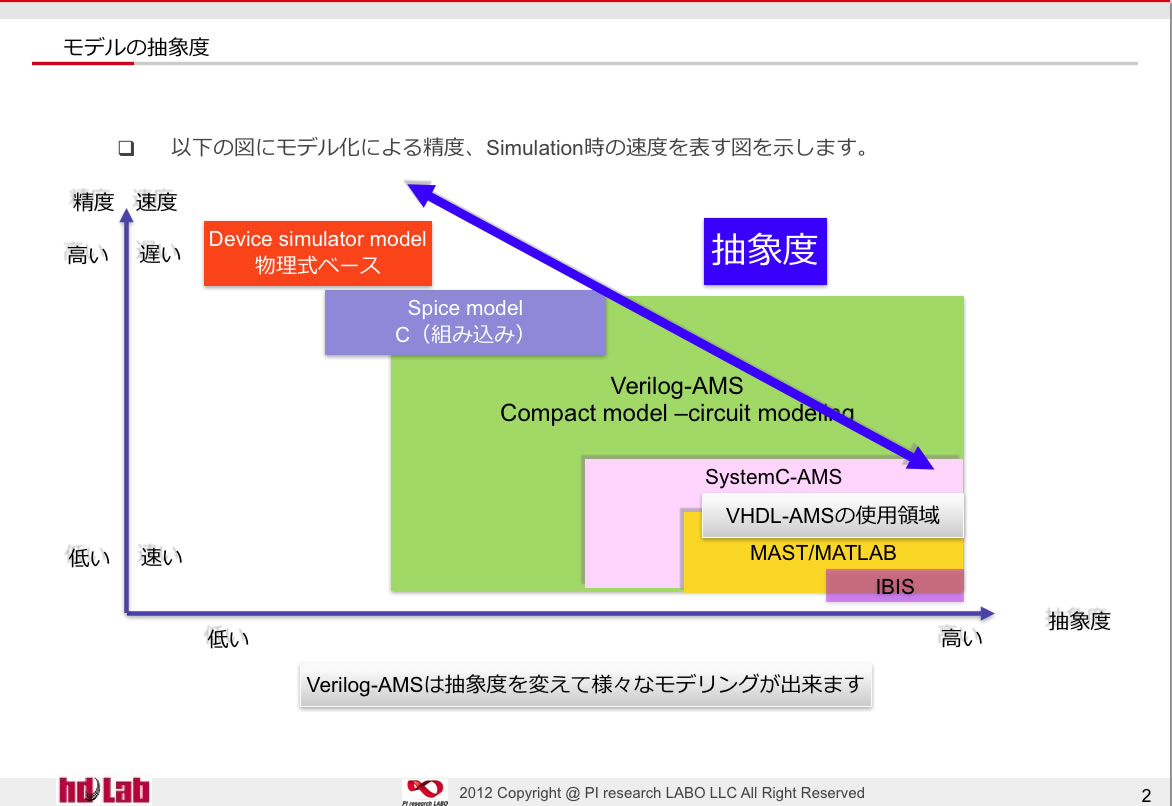

抽象度について

Verilog-AMSやMATLABのユーザは、抽象度という概念がある程度身に付いていますが、VHDL-AMSのユーザはどうも、この概念が欠落してるように見えます。ちなみにSpice Simulatorが変われば、同じモデルを使っても結果が変わるというのは半導体設計者の間では公知の事ですが、VHDL-AMSユーザはこれが理解出来ません。Simulatorの浸透度が原因でこれから理解しなくては行けない事ですが、以下Verilog-AMSで使用しております、講座テキストから

本来Verilog-AMSよりもVHDL-AMSの方が表現力があるはずですが、普及例のVDA FAT-AK30を見ますとほとんどがSystem系の抽象度で収まっていますので、上記のように表しています。Veriog-AMSはCMC(Compact model Concil)のモデリングの標準言語であると同時に回路設計で各社使用例が多くあるので上記のように広いエリアになっています。

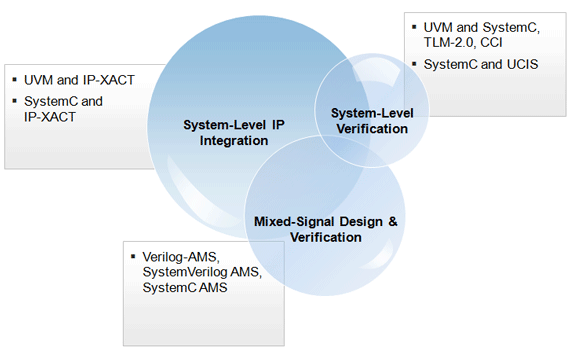

Acceleraについて

Accellera(アクセレラと読みます)というのは、EDA(Electirc Design Automation)の標準化団体で現在以下の設計言語の標準化と管理運営しています。

以下情報、AccelleraのHPより引用させていただきます。

Accellera Systems Initiative Standards and Implementations

- Verification Intellectual Property (VIP)

- Universal Verification Methodology (UVM) 1.1

- Open Verification Library (OVL) 2.5

- Standard Co-Emulation Modeling Interface (SCE-MI) 2.1

- Unified Coverage Interoperability Standard (UCIS) 1.0 (imminent)

- IP-XACT (Q1 2012)

- Intellectual Property (IP) Tagging (launched)

- SystemC

- SystemC Synthesizable Subset Draft 1.3

- SystemC Transaction-level Modeling (TLM) 2.0

- SystemC Analog Mixed-Signal (AMS) 1.0

- SystemC Configuration, Control & Inspection (CCI Requirements)

- Verilog-AMS (V-AMS) 2.3.1

- Open Source Companions:

- SystemC Reference Implementation 2.2

- SystemC Verification Library 1.0p2

- UVM Reference Implementation 1.1

- OVL

Completed IEEE Standards

- IEEE 1076: VHDL Language Reference Manual

- IEEE 1364-2005: Verilog Hardware Description Language

- IEEE 1450.6.1: Open Compression Interface (OCI)

- IEEE 1497: Standard Delay Format (SDF)

- IEEE 1666-2011: SystemC language

- IEEE 1685: IP-XACT

- IEEE 1800: SystemVerilog (SV)

- IEEE 1801: Unified Power Format (UPF)

- IEEE 1850: Property Specification Language (PSL)

よく見てほしいのですがVHDLはありますがIEEE1076.1(VHDL-AMS)はありません。しかしVerilog-AMS(1354-2005)やSystemVerilog(IEEE1800)はありますね。Accelleraが将来計画している標準化は以下です。

気づいた方いるかと思いますが、どこにVHDL(IEEE1076)もないですし、VHDL-AMS(IEEE1076.1)も当然ありません。

以上AccelleraのHPからの参照でした。よりAccelleraの詳細を知りたい方は、以下URLからご確認ください。

Accelleraの活動URL:http://www.accellera.org/activitiesちなみにJEITAで、小島さんの発表で以下の発表資料の中で

- VHDL-AMS is IEEE standard and might be in an academia

- Verilog-AMS might be De Facto standard in the market

- SystemC-AMS will be OSCI standard soon

なんて発表されています。※2009/2010年 IEEE-DASC at DVCcon2010 発表資料より

◆ Verilog HDL(IEEE1364)/Verilog-AMS

- 1984年: ゲートウエイ・デザイン・オートメーション社がシミュレータおよび

- 言語の開発(1990年にCadenceに買収される)

- 1995年: IEEE(IEEE1364-1995)標準化

- 1996年: Verilog-A LRMがOpen Verilog International (OVI)に認証される

- 1998年: Verilog-AMS LRM 1.0がOVIにて認証

- 2000年: Verilog-AMS LRM 2.0がOVIにて認証

- 2001年: IEEE1364-2001標準化

- ※現状1995のバージョンが主流 (現在、SystemVerilogへの移行中)

- 2003年: Verilog-AMS LRM 2.1がAccelleraにて認証

- 2005年: IEEE 1364-2005 /また上位互換のSystemVerulog IEEE 1800-2005

- 2008年: Verilog-AMSにてVerilog HDLの算術関数の拡張等、SystemVerilogの

- AMS対応のVerilog-AMS LRM 2,3が策定される

- 2009年: 最新版LRM2.3.1リリース

◆VHDL(P1076)/VHDL-AMS (P1076.1)

- 1981年:米国国防省によって開発

- 1993年:IEEE標準化 IEEE 1076-1993

- 1999年:VHDL-AMS IEEE1076.1標準化 IEEE1076.1-1999

- 2000年:2000年版標準化 IEEE 1076-2000

- 2002年:2002年版標準化 IEEE 1076-2002

- 2004年:P1076.1.1(分科会)発足

- 2007年:2007年版標準化 IEEE 1076.1-2007

- 2009年:2008年版標準化 IEEE 1076-2008

VHDL(P1076)の枝分かれしたsub comitte(分科会) は以下ですが、すでにIEC(国際電子標準会議)標準から外れている規格があります。P1076.2/P1076.3がIEC標準から外れたそうです。

- P1076 VHDL Analysis and Standards Group (VASG)

- Issues Screening and Analysis Committee (isac)

- P1076a VHDL Shared Variables Working Group (svwg)

- P1076.1 VHDL Analog and Mixed-Signal (vhdl-ams) Working Group

- P1076.2 VHDL Math Package (math) Working Group

- P1076.3 VHDL Synthesis Package (vhdlsynth) Working Group

- P1076.4 Timing (VHDL Initiative Towards ASIC Libraries: vital) Working Group

- P1076.6 VHDL Synthesis Interoperability (siwg) Working Group

Verilog-AMS/VHDL-AMS 比較

比較自体が、ばかげているのですが、Simulatorの対応状況をみれば一目瞭然です。

Verilog-A/MSの対応Simulatorは、ほとんどのSpice Simulatorが対応しています。

VHDL-AMSは、

- Mentor : SystemVision

- ANSYS:Simplorer

- Synopsys:SABER

- Dolphin Integration:SMASH

です。Questa ADMS/ AMS Designerもありますが、Verilog-A/VHDL-AMSを考えると上記のSimulatorになります。

一方でVerilog-A/MSのSimulator

- Cadence: SPECTRE

- Mentor:ELDO

- ANSYS:NEXXIM

- SILVACO:SmartSpice

- Synopsys:Hspice

- Tannar:T-Spice

- BDA:AFS

- Magma:FineSim/FineSim pro

- Dolphin Integration:SMASH

名だたるSpice Simularorがありますね。(紹介できなかったVendor様、またの機会に…)

VHDL-AMSの問題:一番の問題は、抽象度とコンパクトモデルの問題です。

Spiceでは、トランジスタやダイオードがありますが、別のページでSpiceに組み込まれているSpiceモデルは同じでないと紹介しましたが、Verilog-Aに対応したSimulatorとVHDL-AMSでは大きく差が出ています。最新のトランジスタに対応してるのは、Verilog-Aに対応したSpice Simulatorです。(トランジスタモデルのバージョンを確認してみてください)

ちなみにVHDL-AMSでかかれたコンパクトモデル≠Spice組み込みモデルではないのです。さらに抽象度が変えたモデリングの概念のないVHDL-AMSには将来はないように思えます。

Verilog-AMSにはSystem Verilogというパスがあるのですが、VHDL-AMSにはパスがありません。IECがSystem Verilogと言ってる以上SystemC-AMSに活路を見いだすしかありません。と言ってSystemC-AMSに参加してる会社を見ますと、STとかNXPとかヨローッパ系の会社が目立ちます。恐らくVHDL-AMSの次を探してるんでしょうね。

とりあえず、今回はこのぐらいに、Simulation速度とかの問題もありますが、おいおい記載いたします。